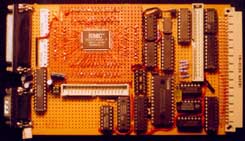

For some time, I've been working on a podule design for Acorn machines with the following basic spec:

- 2 IDE controllers (supporting 4 ATA/ATAPI devices)

- Floppy controller (for 2/4 floppy drives, to 2.88MB)

- SPP/EPP/ECP parallel port

- 2 RS232 serial ports, to 460Kbps

- Optional IrDA infrared support, also possibly HPSIR, ASKIR, Consumer IR and Fast IrDA (4Mbps)

- Optional MIDI support (both take over serial port 2)

- ~512KB flash ROM onboard

- DMA support for IDE, floppy and parallel port, and possibly infrared as well

- All on single width podule, for both Risc PC/A7000 and earlier machines (although problems with backplate space as card provides too many interfaces for one backplate).

- Small software and hardware changes required to support an A3000-style 8 bit podule slot.

The design utilised the FDC37C669 IO controller from SMC, which extra IR features provided by the largely pin compatible FDC37C669FR. Other main components being the flash ROM and an ispLSI2064 programmable logic device from Lattice Semiconductor to provide interrupt control, DMA sharing and general glue logic.

Unfortunately, lack of time on my part prevented me from finishing the project, so I'm releasing it here in the hope that it might be useful to someone. The current status is that I have one prototype that works, and have the designs for the final version which I'm releasing here, which should serve as a useful example of podule design. If anyone's interested in using this design for anything other than general interest or research, please contact me (theo [at@] markettos.org.uk).

The schematics are available here in gzipped PostScript (77K), plain PostScript (710K), PNG (263K) and GIF (915K). Note these bitmap files are big - approximately 10000 by 14000 pixels. If your machine can't handle these, get the PostScript version and run it through Ghostscript to produce something you can handle. The PCB program they were produced on (BPECS32) output the whole schematic as a single A4 PostScript file, and these bitmaps were generated from this at 1200dpi. You might need to do something similar to be able to read the text.

The PLD schematic maps are here as well - they've been converted to GIF format, and can either be downloaded as a zipfile (314K), or browsed individually. The original maps are available on request, although they probably aren't of much use unless you're using Lattice's Synario system.

I'm not currently making the software available, as parts of it are written by other people, and it may be used in other projects. If you need anything specific in terms of software that I might have, or think you might be able to use software developed for this card, let me know.

If you've got any questions about this design, or would like to do anything with it, please feel free to get in touch. I'm retaining copyright on the design, but you may use it freely for educational or non-profit making purposes, and I'll be reasonable if you want to do anything else with it.

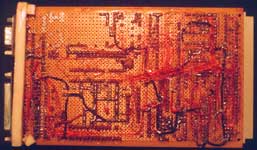

First prototype pictures

Page by Theo Markettos (email at theo [at@] markettos.org.uk), last modified 2002-05-31

Return to my RISC OS pages, or the Arxe software.