A-level Electronics Major Project

# Home Automation System

## Theodore Markettos

25th March 1997

PDF conversion by GhostScript 5.10

Copyright Theo Markettos 1997. This may be used for educational and non-profit making purposes only. The author may be reached at theomarkettos@letterbox.com

## Contents

| Summary                                            | .1 |

|----------------------------------------------------|----|

| Part 1: The microprocessor system                  |    |

| Choice of microprocessor                           |    |

| Rest of microprocessor system                      |    |

| RAM                                                |    |

| ROM                                                |    |

| Modem connection                                   |    |

| Real time clock and timing                         |    |

| Other inputs/outputs                               |    |

| Memory map                                         |    |

| Revisions                                          |    |

| Microprocessor control signals                     |    |

| Clock                                              |    |

| Reset and Halt                                     |    |

| Function code outputs (FC0-FC2)                    |    |

| Interrupt control lines (/IPL0-/IPL2)              |    |

| Bus arbitration control line (/BR, /BG, /BGACK)    |    |

| Asynchronous bus control signals                   |    |

| Address decoding                                   |    |

| I/O decoding                                       |    |

| RAM                                                |    |

|                                                    |    |

| ROM Initial testing                                |    |

| Digital inputs and outputs                         |    |

| Digital output                                     |    |

| Digital input                                      |    |

| Exception vector code                              |    |

| 6800 series bus cycles                             |    |

| 6800 series peripherals                            |    |

| 6821 Peripheral Interface Adapter                  |    |

| 6818 Real Time Clock                               |    |

| 6522 Versatile Interface Adapter                   |    |

| Serial port                                        |    |

| 6850 Asynchronous Communications Interface Adapter |    |

| Data rate selector                                 |    |

| Line drivers                                       |    |

| Interrupts                                         |    |

|                                                    |    |

| Data link                   | 56 |

|-----------------------------|----|

| Transmission                | 57 |

| Transmission filtering      | 62 |

| Receiver filtering          | 64 |

| Receiver amplification      | 66 |

| Rethink                     | 67 |

| Wire link transmitter       | 68 |

| Wire link receiver          |    |

| Amplification               | 72 |

| Signal detection            |    |

| Data link circuit diagram   | 76 |

| Remote control module       |    |

| PIC hardware                |    |

| Remote module software      |    |

| Main routines               | 83 |

| Master control transmitter  |    |

| Master control software     |    |

|                             |    |

| Evaluation                  | 94 |

| Photographs of project      | 96 |

| The microprocessor system   |    |

| Data link and remote module |    |

| Appendix A                  |    |

| Appendix B                  |    |

| Main program                |    |

| Interrupt handling code     |    |

| Exception handling code     |    |

| Definitions file            |    |

| Bibliography and References |    |

| Acknowledgements            |    |

|                             |    |

#### Part 2: The data link and remote module

## Summary

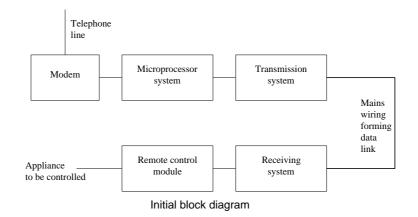

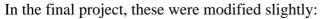

The aim of this project was to build a home automation system so that the householder could dial into their house with a modem, from the office or even the other side of the world, and control their home appliances.

The main part of the system had to be microprocessor based, because of the requirement to communicate intelligently with a person at the other end of a telephone line. A reasonably powerful system was chosen to perform the task competently. This formed a flexible multipurpose system not tied to this project. The modem input was replaced with a computer terminal because I did not have access to two telephone lines for testing.

The main control unit talks to a module fitted in each appliance, which contains a small customprogrammed microcontroller. Originally I intended the module to communicate with the main system over the mains wiring, but problems caused by not having direct mains access meant a wire link had to be used instead. This was designed to be easily converted to a mains link if required.

Overall, the system works, but the software could be substantially improved. This is a large project, so it was not possible to refine it in the time available.

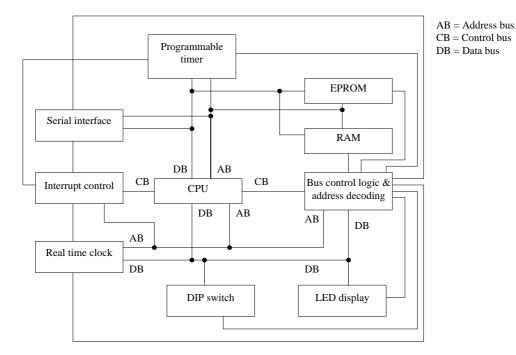

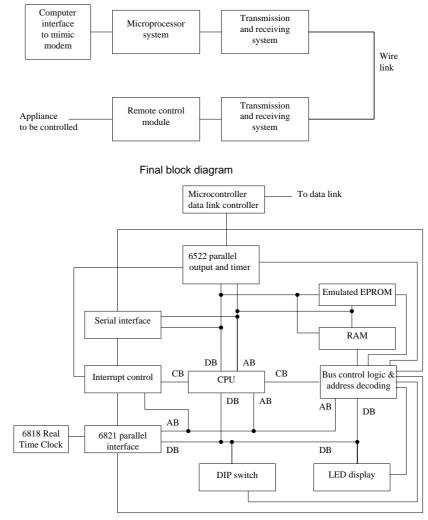

The microprocessor system was split again into a number of blocks:

Initial block diagram of microprocessor system

Final block diagram of microprocessor system

Copyright Theo Markettos 1997. This may be used for educational and non-profit making purposes only. The author may be reached at theomarkettos@letterbox.com

## **Choice of microprocessor**

The main control unit is obviously going to require some intelligence so that it can interpret commands sent along the phone line by modems. While it might just be possible to build a system that used simple logic at the controller end and based the intelligence at the sending computer, it would present its own problems. Such a system would have a program on the transmitting computer offering options such as lights on/off/dim or heating on/off, and convert these to codes which would then be sent along the telephone line. These codes would be in the form that the logic at the other end could understand - for example 10 for lights, followed by a number in the range 0 to 100 to set the intensity. The controller would receive and decode these signals, and then perform the relevant action. This method has numerous drawbacks. Firstly, the system is inflexible, since it can only do what is hard-wired into it. For example, it would be very difficult to set the system to turn the heating on at 6 pm, rather than immediately. There is also no form of error checking - the byte 10 to turn on the lights could get corrupted into 13, which might turn the cooker on - obviously a problem. It also will only work from those computers which have the necessary software installed, since dialling the home control system directly will only allow communication in numeric codes.

The level of intelligence required means some form of programmable logic is required. For this degree of complexity, it seems that a microprocessor or microcontroller is the only solution. Other forms of programmable logic would still suffer from the problems outlined above. A particular type and model of microprocessor/controller needs to be chosen, since, unlike NAND gates each type is basically unique and its individual characteristics need to be taken into account from the earliest design stages. It is very rare that one microprocessor is a 'drop-in' replacement for another, and this would only happen within the same microprocessor family.

In a commercial situation, it would be likely that a microcontroller would be used. For this project, however, this can oversimplify matters. Some microcontrollers simply require programming of their internal EPROM or EEPROM memory, the provision of a power supply and a few clock components, and you have a full system, including parallel and serial outputs, a real time clock, and plenty of onboard memory, with virtually no external electronics at all. In addition, the project needs to be assembled on solderless breadboard. This will only fit dual-in-line ICs, which creates problems since most microcontrollers come in PLCC (plastic leaded chip carrier), PGA (pin grid array) or surface mount packages, which will not fit in the board. In most cases reliability problems may arise if an adaptor has to be made to convert these packages to a DIL pinout.

This means a choice of microprocessor has to be made. Many of the fairly low powered processors originated in the early 1970s and, while still available, have not been developed recently. It is preferable if the project uses a processor which is still having new versions added to the range, and so is not obsolete. The slower 4 and 8 bit processors also may not have enough power to be able to handle the task easily. For example, many 8 bit computers cannot receive data through the serial port faster than 9600 bits per second because they simply cannot keep up with the incoming flow of data. It is certainly true that not all 8 bit microprocessors will have this problem, as modern versions have been streamlined to work at upwards of 20 MHz. However, these high frequencies generally cause havoc on breadboard, where the board capacitance is quite high.

This frequency problem is also true for 16 and 32 bit processors as well, as they are generally designed for high power applications, which also employ high clock speeds. However, these are generally more efficient, so that a 16 bit processor running at the same clock speed as an 8 bit processor will be able to shift data around faster, not least because of its bigger bus size.

It would be possible to use modern, high powered RISC processors such as the ARM, SPARC, PowerPC or MIPS systems. However, these are all 32 bit processors, so would require ROM and RAM 32 bits wide. Using standard static RAM and EPROM chips, this would require a total of eight 28 pins ICs just to provide storage. In addition, there is still the problem that none of these are available in DIL packages.

This leaves 16 bit processors, of which there are two main families, the Motorola 68000 family and the Intel 80x86 family (otherwise known as the Intel iAPX family). The simplest versions of the 80x86 family which are available in DIL packages are the 8086, which has a 16 bit data bus, and the 8088, with an 8 bit external data bus but a 16 bit internal data bus. This means the two chips are identical from a software point of view, but the 8088 requires less wiring. The 68000 family is similar, with the 68000 (16 bit data bus) and 68008 (8 bit data bus) being available in DIL packages. The Intel family have a multiplexed address and data bus, which means that external logic is required to demultiplex them. They also have a 'segmented architecture', which means that the entire memory is not available at the same time.

For these reasons, the 68000 family was chosen. This leaves a choice between the 68000 and 68008. The 8 bit bus requirement means that instruction execution times on the 68008 are double that of the 68000, since, to access an instruction it has to perform two memory reads. This means the power of the processor is approximately halved. For this reason the 68000 was chosen.

Due to the nature of a microprocessor system, a large amount of hardware has to be in place before anything can work, but once this basic hardware is present, new sections can be tested as they are added on.

## **Rest of microprocessor system**

Having decided to use the 68000 microprocessor, decisions now need to be made on the peripherals that will be attached to it. It is best to decide on this from the start, so that they can be taken into account when other parts of the system are designed.

#### RAM

The system needs some RAM to store data that it is working on. There are two main types of high density RAM used in computer systems - static and dynamic RAM. Static RAM holds the data in arrays of flip-flops, while dynamic RAM uses large numbers of capacitors. The problem with these capacitors is that their charge leaks across the dielectric, so needs to be refreshed every few milliseconds. DRAMs also have a multiplexed address bus, in which the row and column addresses of the capacitor matrix are strobed in sequentially. This means the access cycle is very complicated, with critical timing requirements. Not only does this require a lot of logic to generate the required cycle, but also the large currents drawn and fast signals mean that noise is a real problem, especially on the high capacitance breadboard. This is why most modern production computer systems have the RAM mounted on a four or six layer PCB. It would be possible to utilise ready made memory cards, such as SIMMs, but the problems with timing would still remain.

By contrast, SRAMs are reasonably easy to use, they don't have a multiplexed address bus, so have no major timing problems. They are also available with an 8 bit wide data bus, which means that only two RAM ICs are required for the 68000's 16 bit data bus. Looking through a supplier's catalogue, shows that there is not a huge choice of suitable devices for breadboard mounting. There are a large number of very fast (~20ns) chips, which are designed as external cache RAM for advanced microprocessors, but their surface mount packages mean they will not fit on breadboard. There are three possible sizes of SRAM: 8 Kbyte, 32 Kbyte, and 128 Kbyte. Since two chips are required, it seems that 32K or 128K devices would be excessive, and there is a large price difference between them and the 8K devices. It was therefore decided to use two 8K 6264 chips to give 16K of RAM.

#### ROM

A ROM is required to store the main program code. The initial thought for ROM would be to use EPROM (Erasable Programmable Read Only Memory), which can be programmed in a special programmer, and can be erased by exposure to 257.3nm ultraviolet light for about 20 minutes. The EPROM is then inserted into the microprocessor system breadboard, and the program can then run. The delay means that every time the program is modified, there is a 20 minute wait before it can be tested. This is obviously not ideal.

An alternative is EEPROM (Electrically Erasable Programmable ROM), which can be erased in a few seconds with a voltage applied to it. This is better, but these devices are expensive, and require removal from the breadboard to be programmed.

In the commercial market, EPROM emulators are available, which consist of a box which plugs into the socket where an EPROM would go, and connects to a computer. The box holds a static RAM, which can be programmed by the computer and appears to be an EPROM from the microprocessor's point of view. These are very expensive, and here two would be required. *Copyright Theo Markettos 1997. This may be used for educational and non-profit making purposes only. The author may be reached at theomarkettos@letterbox.com*

However, since the microprocessor system is being designed from scratch, an EPROM emulator can be built on breadboard, to which the address, data and control buses can connect it to the rest of the system.

The ROM system therefore requires a size of static RAM to be chosen. Because of the price difference, 8K devices were again chosen to give 16K of ROM. Since they are mostly pin compatible, they can be replaced with 32K devices if required.

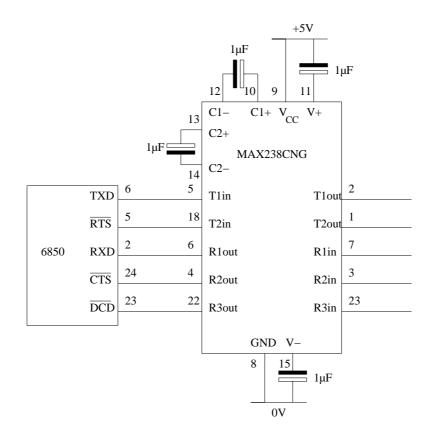

#### Modem connection

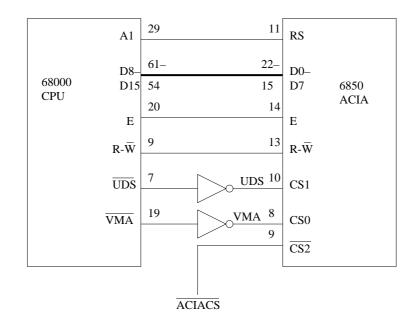

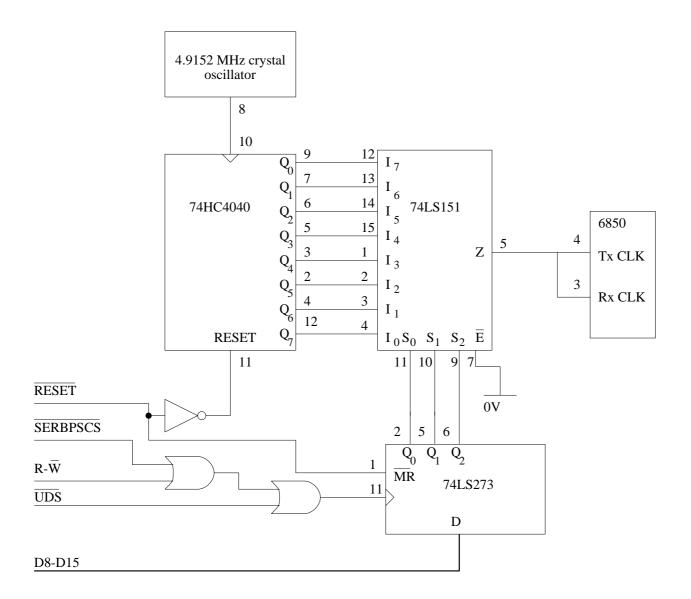

Modems invariably communicate with a microprocessor system using a serial link, as this is the way the information will be sent through the telephone system. The parallel-based microprocessor system needs some form of converting parallel data to a serial signal and back again. This could be done with discrete logic, but the asynchronous nature of the RS232 serial communications used presents problems. It is much easier to use a dedicated LSI IC to perform the conversion, and they often have extra features such as error detection as well. There are a large number of these devices available, many of which are designed for particular microprocessor architectures. Those that are not generally require great care to ensure read and write cycles are compatible with the 68000. The 68000 family has its own array of serial controllers, such as the 68562 dual universal serial communications controller, or the 68681 dual universal asynchronous receiver/transmitter. While these are designed to interface with the 68000's bus, they are expensive and complex. An alternative is to look to the 6800 family, which were the 8 bit predecessors of the 68000. The 68000 can drive 6800 series peripherals, by modifying its bus cycle and effectively accessing the bus at 1 MHz instead of 8 MHz. This gives a performance decrease, but when the maximum data rate modems can handle is 28800 bits per second, this should not be a problem. The 6850 ACIA (asynchronous communications interface adapter) would be seem to fit this application, and they are cheap and widely available.

#### Real time clock and timing

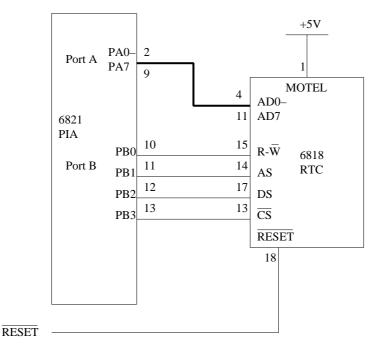

The system needs an accurate way of telling the time, so that commands to activate appliances at a particular time can be accepted. It would be possible to derive such a signal from the microprocessor clock, but a hardware system consisting of dividers would not be flexible enough, and a software based system could not keep the time to a reasonable standard of accuracy. However, dedicated ICs are available for this purpose, mainly to keep the time and date in desktop PCs. Of the field available, a look through a supplier's catalogue shows that most are quite expensive. One that is not is the 146818, which is a CMOS part and also happens to be a member of the Motorola 6800 family, and therefore this was chosen. Once I had received the data sheet, I found out that this uses a multiplexed address and data bus. With this device, the address is placed on the bus and then address strobe (AS) taken high. AS is then negated, and then the data read or written in conjunction with data strobe (DS) and read-write (R-/W). While the 68000 has pins with these labels, they do not perform the same function as those on the 6818, and it cannot multiplex its bus. The 6818 therefore cannot be connected directly.

The data sheet gives two possible alternatives for interfacing with a non-multiplexed bus. One is to use the bus control signals of the processor with some combinational logic to simulate a multiplexed bus cycle by writing to the device twice. An example is not shown for the 68000, and this method seems quite risky because it is very difficult to troubleshoot it if it does not work. The alternative given is for a single chip microcomputer, and involves simply connecting

the address/data bus to one input/output port, and the control signals to another. This seems a more reasonable situation, where the processor can control the bus signals directly, which is a simpler situation to debug.

This requires another device to provide the link between clock chip and processor. Sticking to the simple and cheap 6800 family, the 6821 provides two 8-bit bidirectional ports, which would be enough to handle the 11 signals from the 6818.

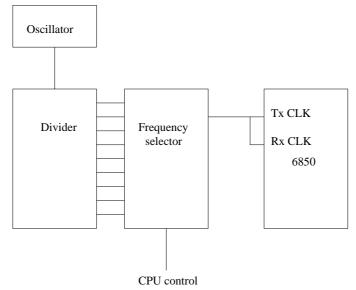

In addition to the real time clock, which is updated once a second, it is useful to have a fast timer, for purposes such as serial input/output, frequency measuring, etc. The 6840 Programmable Timer Module is a flexible timer chip which performs this function. It contains three 16-bit counters which count at up to 8 MHz with many different control settings.

#### Other inputs/outputs

A port is required so that the system can communicate with other devices in the house. This will require only a few bidirectional lines, so could be provided by the spare lines on the 6821.

For the purposes of testing, it is useful to have a simple set of inputs and outputs, such as a bank of switches and LED display. To aid their simplicity, it is best if these are made from standard TTL components. These don't require any complicated control signals and are much faster than the more flexible LSI devices.

## **Memory map**

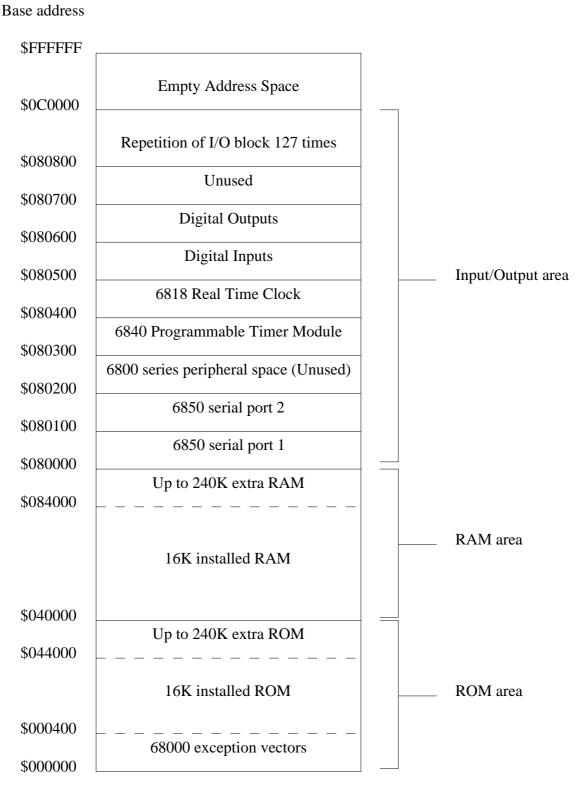

From this information a map showing which devices are allocated to which memory addresses is required. Since the 68000 series uses memory mapped I/O, this includes all I/O devices as well as ROM and RAM. At the start of the project, a provisional memory map was drawn up:

Note: \$ is used to denote a hexadecimal number

Copyright Theo Markettos 1997. This may be used for educational and non-profit making purposes only. The author may be reached at theomarkettos@letterbox.com

The choice of up to 256K of each of ROM, RAM and Input/Output (I/O) space is deliberate, giving a total address space requirement of 768K, which will fit into the 1Mb address space of the 48-pin 68008. This is so that the same software could be used on a system based around either the 68000 or the 68008 with little or no modification. I/O does not really need 256K of space, but an equal allocation to each sector saves on address decoding logic.

ROM has to be present at location \$000000 and upwards since the 68000 reads the address to jump to on a reset from an address table stored in the first 1K of memory, from \$000 to \$3FF. The 16K of ROM therefore extends from \$000000 to \$00003FFF. To allow more ROM to be fitted easily, an empty space is left between \$004000 and \$040000, where up to 240K of additional ROM can be fitted.

RAM is therefore fitted from location \$40000 to \$43FFF. There is nothing that specifies where RAM has to be since only the ROM contains references to it, which can be changed. Again this can be expanded to 256K if required.

Likewise, there is no specific reason why I/O is placed in a chunk from \$80000 to \$C0000. The I/O space is split into a number of sub-sections, each of which is allocated to an individual chip. The figure of 256 bytes per device is, for the most part, excessive, but allows the same allocation for each one, again saving on logic. The space is deliberately organised, so that the first four devices require a synchronous VPA/VMA access (which will be dealt with later), while the higher four can be accessed using normal bus cycles. This means that when I/O is selected, the state of address line 10 (A10) signifies which type of access is required (low for VPA, high for asynchronous).

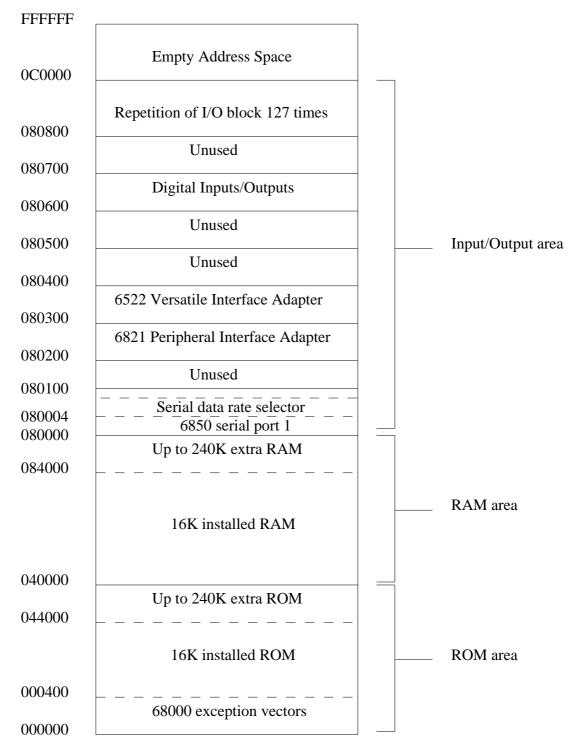

#### Revisions

The memory map was later revised for a number of reasons. Firstly, it was decided that a second serial port would be unnecessary, since more complicated programming would be required to drive both simultaneously. The space in the memory map is left free so that another can be installed if required, but this is overkill for this project. After receiving the 6818's data sheet, the 6821 had to be inserted between the 6818 and the processor to simulate a multiplexed bus. This also provides a few spare general purpose digital input/output lines.

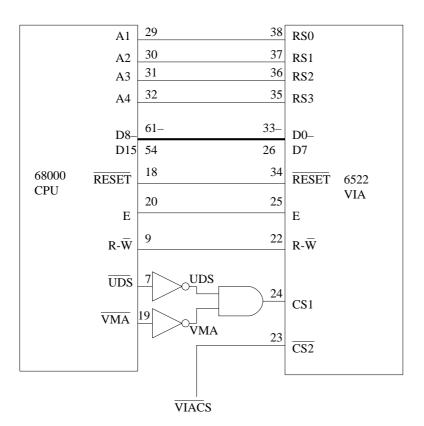

The decision was taken to replace the 6840 with a 6522 Versatile Interface Adapter (VIA), which performs most of its timing functions, but has the advantage of two 8-bit input/output ports. These ports provide more lines to communicate with the other devices in the house, and are more flexible than using the spare lines from the 6821. This uses the same bus protocol as the 6800 series, but is from Rockwell instead of Motorola.

The digital out and digital in are wasting a block of address space, since they only work if written to or read from respectively. These were combined onto one address, \$80600, so that a read examines the input, while a write outputs data.

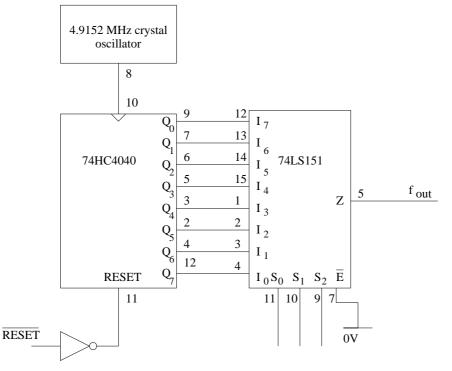

The 6850 which drives the serial port has a very limited way of selecting transmit and receive rates, which does not allow all those data rates which could be output by a modem or computer. It therefore needs some external circuitry to select the data rate under processor control. Since the 6850 occupies two addresses, the external circuitry should be in this area (\$80000 to \$800FF), but clear of these two addresses. The simplest way is for the 6850 to be at \$80000 and \$80002, and the data rate selector to be above this at \$80004. The reason why these addresses go *Copyright Theo Markettos 1997. This may be used for educational and non-profit making purposes only. The author may be reached at theomarkettos@letterbox.com*

up by two instead of one is that the 68000 is a 16-bit processor but each address is treated as 8 bits, so \$80000 refers to the top half of the data bus (D8-D15) and \$80001 to the bottom half (D0-D7). It is simpler to connect only one half of the data bus to the 8-bit bus of the 6850 and refer to it as the consecutive 16-bit addresses \$80000 and \$80002 than try to mess around with multiplexing, connecting the top half of the bus to the chip when \$80000 is accessed and the bottom half when \$80001 is accessed. Thus the register select line of the 6850 is connected to A1.

The revised memory map is as follows:

Base address in hex

*Copyright Theo Markettos 1997. This may be used for educational and non-profit making purposes only. The author may be reached at theomarkettos@letterbox.com*

## **Microprocessor control signals**

As well as the two major address and data buses, the microprocessor has a number of control signals which need to connected in the correct way before it will work. Most of these are dealt with below. A full list is given in Appendix A figure 3-1.

Note: The terms assertion and negation have been used here to avoid confusion between active low and active high signals. They state whether a signal is active or not independently of whether it is represented by a high or low voltage. / is used to denote an active low signal, as in /DTACK, which is also referred to by its proper notation,  $\overline{DTACK}$ , where possible.

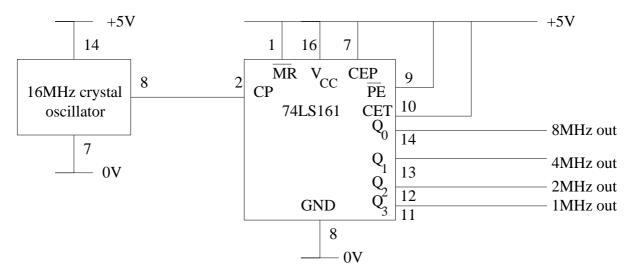

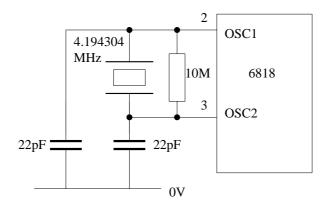

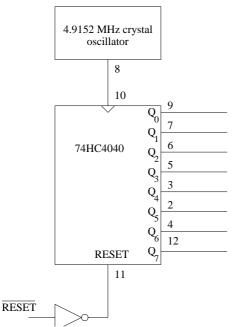

#### Clock

The device in use is an MC68000P8, which means it is rated at 8 MHz. According to the 68000 User's Manual, this means it can be clocked with a single phase clock between 4 and 8 MHz. Since the project is being built on breadboard, it is advisable to choose the lowest possible frequency, as the high capacitance of breadboard may cause significant problems with high frequency signals. For this reason, 4 MHz seems the optimum frequency. The 68000 uses dynamic registers, so a lower frequency would mean that there is the possibility of them being corrupted.

This 4 MHz has to derived from some sort of oscillator. This could be a simple RC oscillator, but the frequency of this is not precise, and will drift with temperature. This prevents it being used for precise timing. An alternative is to use a crystal based system. Due to the problems found using an external circuit to drive a discrete crystal in the previous project, it seems better to avoid them and use a crystal oscillator which is guaranteed to work.

The problem with using a crystal oscillator directly is that they produce a waveform which is not necessarily square, and does not have a 50:50 mark:space ratio. This is vitally important in a microprocessor system, where the clock may be split up within the processor into different phases. The simplest way to overcome this is to feed the clock into a divider, so that an even square wave it produced as long as the clock period is constant, which it is from a crystal oscillator. This requires an oscillator of twice the desired frequency. To allow an 8 MHz signal to be used if required, a 16 MHz oscillator was chosen.

This has to be fed into a divider, which can be any binary counter. The 74LS161 happened to be to hand, which is a 4 bit synchronous counter. The synchronous nature means that race hazards will not occur, and the 4 bits mean that 8, 4, 2 and 1 MHz frequencies can be produced. It was connected as follows:

The inputs taken high disable some of the extra features of the counter that are not required.

There was some ringing on the output, probably due to the high capacitance of the breadboard. This could be rectified by using some form of RC network on the line if this causes a major problem.

The 4 MHz output ('161 pin 13) was connected to the 68000 clock input (pin 15).

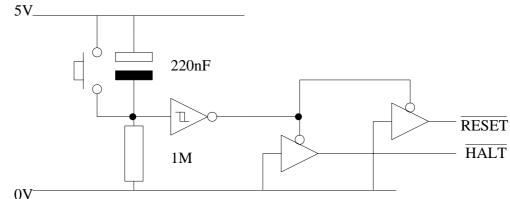

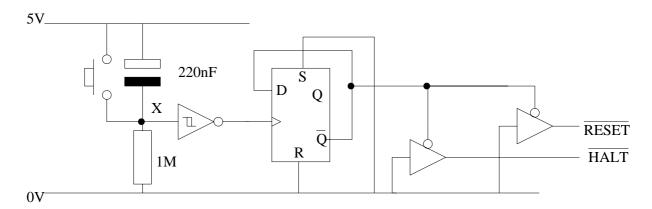

#### **Reset and Halt**

The UM states that both /Reset and /Halt pins should be asserted for 100ms for a proper external reset. There is a need for the system to be reset at power on as well as when a button is pressed. As in the previous project, an RC network can be used to provide a pulse at power on.

Initially there is no net charge on the capacitor, so no voltage across it. When the power is applied, it gradually charges up, causing the voltage across it to increase. This causes the input to the Schmitt Trigger to drop, giving a low-to-high transition on the output. This is precisely the change required on the Reset and Halt lines. A switch across the capacitor will discharge it if pressed, so it behaves as at power on, causing a reset. This also has the effect of debouncing the switch.

However, these signals are bidirectional, so can be driven by the processor as well as external circuitry. It is therefore not a good idea to connect a standard logic gate to them, because the gate will always sink or source current, causing problems if the processor drives the line at the same time.

The alternative is to use tristate or open-collector drivers, which will behave as an open circuit if they are not enabled. Open-collector drivers only have the ability to pull the line low, while tristates can pull it high or low without external resistors.

Tristates were therefore chosen because they have more flexibility, so the spare gates in a tristate chip do more than the spare gates in a open-collector driver chip.

The RC network was connected to tristates to perform the reset as shown below.

It is also useful if the reset button could toggle the reset state, so that one press starts a reset, and the next allows the processor to start execution. Many forms of bistable could be used for this operation, but the simplest from a design point of view is to use a D flip-flop with /Q connected to D. On each successive rising clock edge, the output will change state. A D flip flop, on a 74LS74A, was connected in this way between the Schmitt Trigger and the tristates:

Unfortunately, this prevents the power-on reset from working! As a coincidence, the RC network before the flip-flop now performs the function of debouncing the reset switch. The simplest way of overcoming this is to use another RC network and Schmitt Trigger, which is ORed with the output of the flip-flop.

The wired-OR feature of /Reset and /Halt can also be used, very simply, by using another switch to pull /Halt low to temporarily freeze the system. Debounce is not really required because the halt function in any case is a cumbersome way of stopping the system. This could be added if it was required.

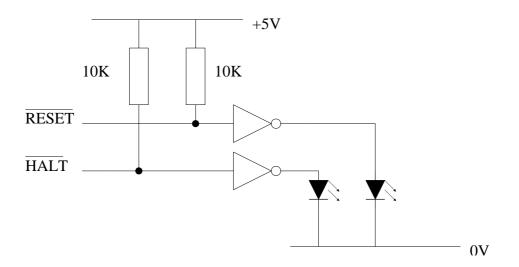

Indicators were put on both /Reset and /Halt to show their current state. Since both these lines are open-drain, when not asserted they are floating. Pull-up resistors were put on them to prevent any noise affecting their state:

#### Function code outputs (FC0-FC2)

These three outputs show the function the processor is currently performing (supervisor or user mode, program or data access). In a more complex system they could be used to protect privileged areas of memory or expand the address space, but here they will just be taken to LEDs via buffers to show their state.

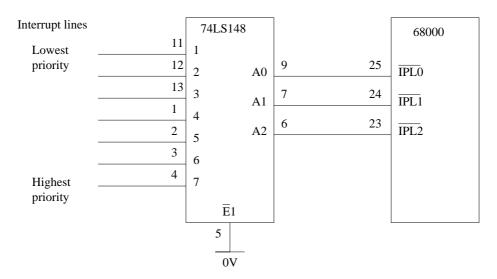

#### Interrupt control lines (/IPL0-/IPL2)

These signal to the processor if an interrupt is asserted. Interrupts will be ignored for the moment until the rest of the system is working, so they will just be taken high.

#### Bus arbitration control line (/BR, /BG, /BGACK)

These lines allow other devices to control the address, data and control buses, for example in multiprocessor systems. This is a very basic system, so they are not needed. They could be used in the EPROM emulator system, except that for another device to access the buses, the cooperation of the processor is required. If the processor has crashed due, say, to a corrupt program, it may not be possible to access the bus to correct that program. To disable them, input /BR and /BGACK are taken high.

#### Asynchronous bus control signals

#### Inputs: Bus error (/BERR) and data acknowledge (/DTACK) Outputs: Address strobe (/AS), read/write (R-/W), and upper and lower data strobes (/UDS and /LDS respectively)

These signals control the flow of data on the buses. A condensed version of the many pages of timing diagrams in the User's Manual is as follows:

#### **Read Cycle:**

- 1 R-/W set high (read), function code outputs show type of access (see above)

- 2 Address placed on address lines

- 3 Address strobe (/AS) asserted to show the address is valid

- 4 Data strobes asserted as required (/UDS shows data is required on D8-D15, /LDS shows data is required on D0-D7 of data bus)

- 5 The processor then waits for /DTACK to be asserted, which signals the receiver has put the data on the data lines.

- 6 Processor stores the data and negates the bus control signals

A write cycle is similar except that data is flowing in the opposite direction, so it is up to the device being written to find out when the data is valid and latch it. It should assert /DTACK to say it has done so.

Unfortunately, none of the RAM being used has any form of acknowledge signal, so this twoway 'conversation' cannot take place. This is also true of most TTL logic, and microprocessor support devices not designed specifically for the 68000 bus. The /DTACK signal is required because otherwise the processor will wait forever for a non-existent acknowledge signal.

An alternative is to wait a long enough period of time until the device being accessed will have responded, and then assert /DTACK. This destroys the two-way nature of the system, as the processor has no way of knowing whether the data has been transferred successfully, but it is the only simple way of making the system work.

The initial thought for a delay circuit is one using RC decay such as the one below:

This was investigated for the previous project, and it was found that it would not respond to fast signals. The signals here are slower than those involved when the RC circuit was tested, but it still may be unpredictable. An alternative would be to use a digital delay line which will delay the signal by a precise time. These are expensive, and are overkill since all that is required is to produce a pulse after a certain time, not reproduce an entire signal exactly as it was entered.

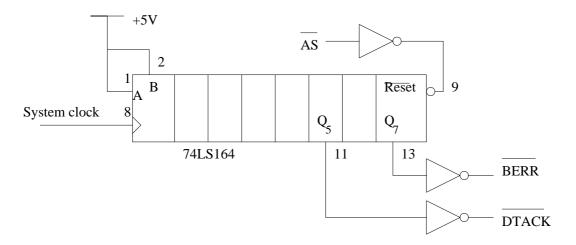

With a bit of lateral thinking, another idea emerged. This was to use a shift register as a delay line, which is triggered by the relevant bus signals. The basic principle is as follows.

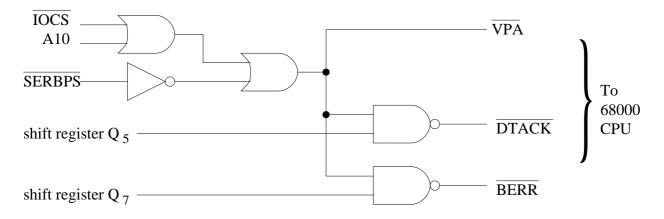

When the bus is not being accessed, the shift register is held in reset. Once a bus cycle begins, the reset is released, and ones begin clocking through under control of the system clock. One of the outputs of the shift register is designated DTACK, so that when a one reaches it, it is inverted and triggers /DTACK, thus ending the bus cycle. This is shown below:

The 74LS164 is a serial-in parallel-out shift register with master reset which suits this purpose. It has two inputs which are internally ANDed together. If connected together, they behave as one input.

According to the timing diagram above, the /AS signal is the first asserted (taken low) when a bus cycle begins. The '164 has an active low master reset, which is the reverse of the state on /AS. Therefore /AS needs to be inverted and then taken to the master reset of the shift register, which will enable it as soon as a bus cycle starts.

Bearing in mind the timing problems involved with breadboard, it was decided to make the processor perform a large number of 'wait-states' for each bus cycle by not asserting /DTACK for some time, thereby slowing the whole system down and increasing reliability. This gets around the limitation that the processor cannot be reliably clocked below 4 MHz.

Thus DTACK was taken from  $Q_5$  of the shift register and inverted to form /DTACK which is taken to the processor. In actual fact, /DTACK is an open collector input so that more than one device can assert it at once. This could be implemented with a tristate as with /RESET but, since only one signal drives it, there is little point in this.

/BERR is the bus error signal which alerts the processor that something has gone wrong on the bus. This can be conveniently connected to  $Q_7$  of the shift register, so that if /DTACK is, for some reason, not asserted then two clock cycles later /BERR will prevent the processor from waiting forever.

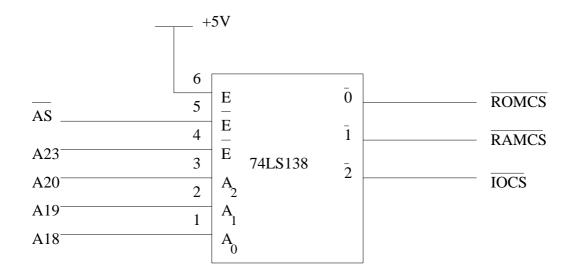

## **Address decoding**

The memory map has to be converted into a logic system which will accept the value on the address bus and generate the relevant chip enable signals. This is called the address decoding circuit.

The decoding can be split up into two main chunks. Firstly, the system needs to decide whether ROM, RAM or I/O is being accessed. If I/O is accessed, it then needs to work out which device should respond.

The initial decoding is shown by the following truth table:

| A19 | A18 | Function |

|-----|-----|----------|

| 0   | 0   | ROM      |

| 0   | 1   | RAM      |

| 1   | 0   | I/O      |

| 1   | 1   | Empty    |

To provide compatibility with the 68008, A20-A23 are ignored. This decoding could be performed by discrete logic gates, but it is simpler to use a dedicated 1 of 4 decoder chip. The 74LS139 contains two of these, but since the other half of the chip would remain idle, it seems better to use a 74LS138, which is a 1 of 8 decoder. If A20 is used as the most significant input, another four address areas of 256K each are made available. These would not be compatible with the 68008, but could be used for further expansion if required.

Thus the truth table now becomes:

| A20 | A19 | A18 | Function                       | Signal name |

|-----|-----|-----|--------------------------------|-------------|

| 0   | 0   | 0   | ROM                            | /ROMCS      |

| 0   | 0   | 1   | RAM                            | /RAMCS      |

| 0   | 1   | 0   | I/O                            | /IOCS       |

| 0   | 1   | 1   | Reserved for further expansion |             |

| 1   | х   | x   | Reserved for further expansion |             |

The signal names are the names the output signals will be known by from now on. The '138 has active low outputs, but this does not matter since most chips have a combination of active high and low chip select inputs. Those not required can be taken to the relevant supply rail. The '138 is also useful because it has two active low and one active high enable input. If these are not activated, all the outputs are held high, disabling all devices. According to the 68000 User's Manual, the /AS output is asserted to signify the address is valid. Therefore this needs to be taken to an active low input, so that the devices are not enabled when the address bus is changing state, which could lead to spurious chip selects being produced. Address line A23 also needs to be low, as when high it signifies an interrupt acknowledge cycle is in progress (more on this later), and the above allocations do not take it high.

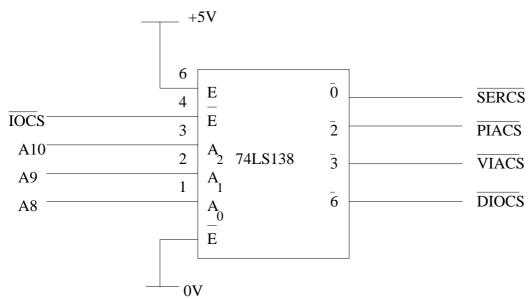

#### I/O decoding

If /IOCS is asserted, an access to an address in the range \$80000 to \$BFFFF is in progress. Further address decoding is required to determine which I/O device is being accessed. The memory map can be converted into the following truth table:

| A10 | A9 | A8 | A2 | Function                                                       | Signal name |

|-----|----|----|----|----------------------------------------------------------------|-------------|

| 0   | 0  | 0  | 0  | Serial port ACIA                                               | /ACIACS     |

| 0   | 0  | 0  | 1  | Serial data rate (bits per second) select                      | /SERBPSCS   |

| 0   | 0  | 1  | х  | Space for second serial port (not fitted)                      |             |

| 0   | 1  | 0  | х  | 6821 Peripheral Interface Adapter (PIA) - 6818 clock interface | /PIACS      |

| 0   | 1  | 1  | х  | 6522 Versatile Interface Adapter (VIA)                         | /VIACS      |

| 1   | 0  | 0  | x  | Unused                                                         |             |

| 1   | 0  | 1  | x  | Unused                                                         |             |

| 1   | 1  | 0  | х  | Digital Input/Output                                           | /DIOCS      |

| 1   | 1  | 1  | х  | Unused                                                         |             |

The majority of this decoding can be done with another 74LS138.

Copyright Theo Markettos 1997. This may be used for educational and non-profit making purposes only. The author may be reached at theomarkettos@letterbox.com

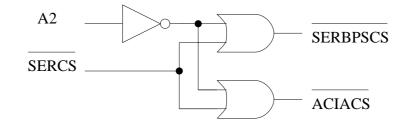

This will not generate the /ACIACS or /SERBPSCS lines, but only a general serial address space access output. This will require external logic to convert it into these two lines.

From the truth table above:

ACIACS = SERCS  $\cdot$  /A2 /ACIACS = /(SERCS  $\cdot$  /A2) = /SERCS + A2

SERBPSCS = SERCS • A2 /SERBPSCS = /(SERCS • A2) = /SERCS + /A2

Therefore:

## **RAM** and **ROM**

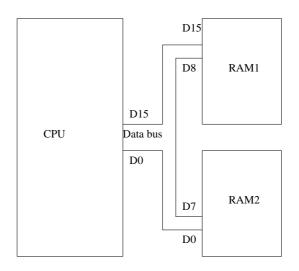

The interfacing of RAM and ROM to the CPU now needs to be considered.

## RAM

The RAM is based on two 6264 devices, which each have eight data lines, thirteen address lines, two chip select signals (CS and /CS), a write strobe (/WE) and an output enable pin (/OE). Since the two devices need to form a block 16 bits wide, one needs to provide the high data lines and the other the low data lines:

As the data bus is 16 bits wide but addresses each hold 8 bits, address line A0 does not exist, as this refers to one or other half of the data bus. Therefore the RAM address lines have to be connected to the next CPU line up i.e RAM:A0 - CPU:A1, RAM:A1 - CPU:A2 etc. The 68000 is big-endian, which means that when storing a 2 byte word it will store the high byte at the lower address, and the low byte at the address above it. Therefore RAM1 will hold the byte at 00, RAM2 will hold the byte at 01, RAM1 will hold the byte at 02 and so on.

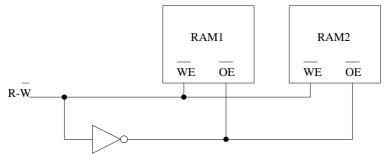

This just leaves the control signals. The address decoding circuitry produces /RAMCS, which goes low to signify an access. This matches with /CE, which enables the chip when it is low. There are no further select signals, so CE can be taken permanently high. This is the same for both RAM chips.

The initial idea to handle /WE and /OE was to connect /WE to R-/W, so that a write (R-/W low) activates the write enable, and /OE to an inverted R-/W, /R-W, which will allow a read to activate the outputs.

*Copyright Theo Markettos 1997. This may be used for educational and non-profit making purposes only. The author may be reached at theomarkettos@letterbox.com*

Unfortunately, a problem emerged because the data strobes /UDS and /LDS are not involved in this. Therefore if a write is performed, the RAM may latch the data before it has become valid.

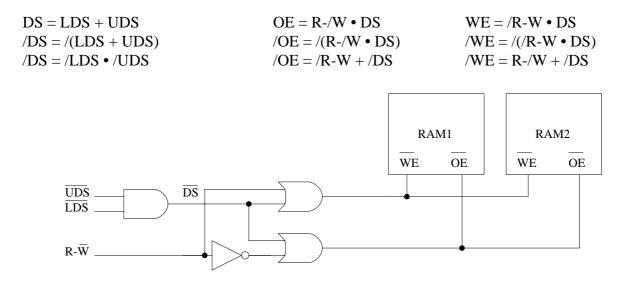

Therefore an improvement needs to be made in this circuit to accommodate /UDS and /LDS. A general data strobe (/DS) was then generated by logically ORing the two signals together, and this fed into a series of gates to provide /WE and /OE.

This does ensure the data is valid before it is written. However, a glance through the 68000 User's Manual showed that if a byte is written to the memory, the rest of the data bus will contain invalid data. With the current system, that invalid data will be stored in the RAM alongside the correct data on the other half of the data bus.

This is the only cycle that causes problems. A byte read is fine because the CPU will ignore the unwanted half of the data bus.

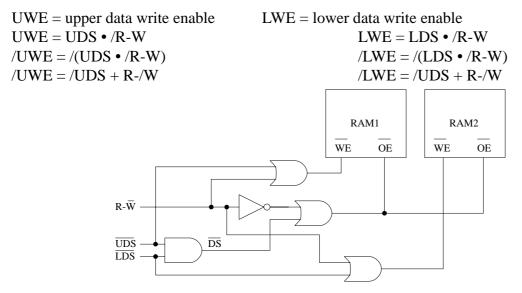

Therefore, the /WE needs to be separate for each RAM chip. The 68000 uses the /UDS and /LDS lines to signal which half of the data bus is being accessed, or if both are being used simultaneously, in a word read or write operation. /OE can be as before since the unwanted half of the data bus is ignored during a byte read cycle.

Copyright Theo Markettos 1997. This may be used for educational and non-profit making purposes only. The author may be reached at theomarkettos@letterbox.com

#### ROM

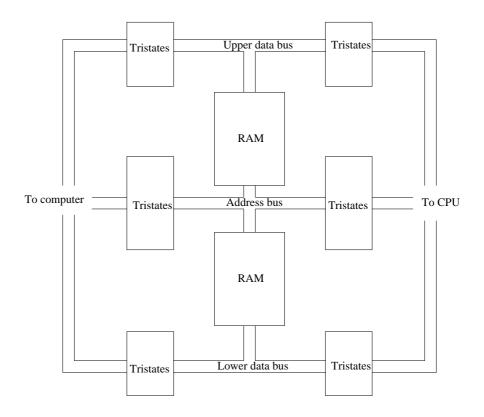

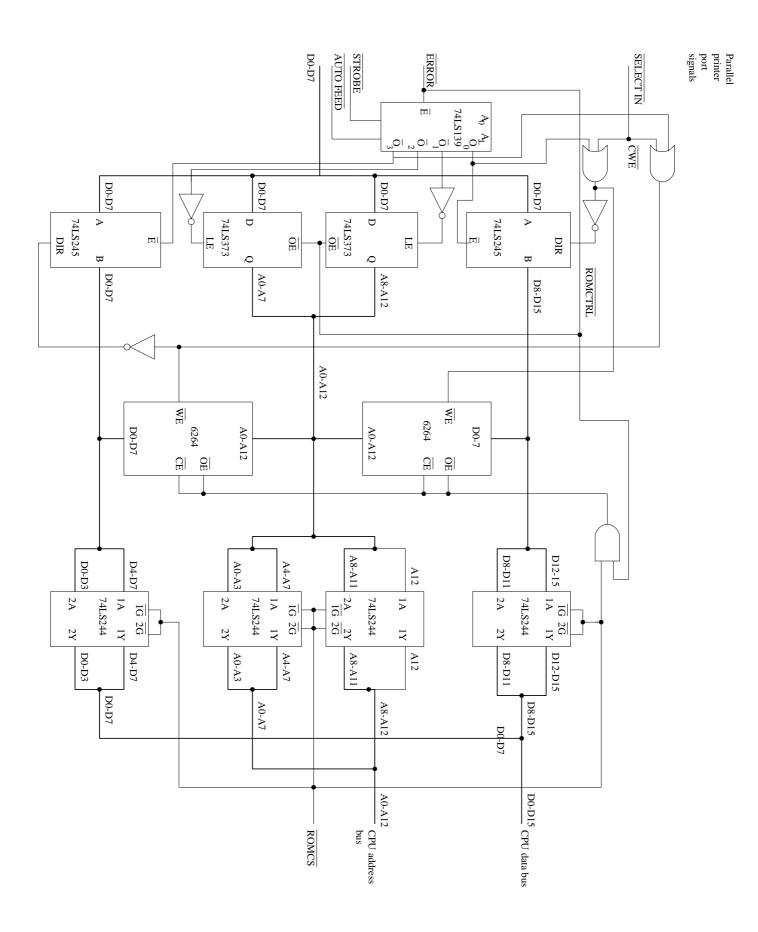

The ROM in this system is composed of two 6264 static RAM chips which can be read and written to by the programming computer, but only read by the microprocessor system. Since the 6264 has only one data bus and one address bus, some logic is needed to decided what is accessing it and connect the accessing address and data buses to the RAM chip. It would be possible to use dual-ported RAM, which has two separate address and data buses, but this is expensive, and it is unnecessary since there in no need to program the RAM while the processor is running a program stored in it. This would, in most cases, confuse the processor and cause it to crash. The block diagram of the arrangement is shown below:

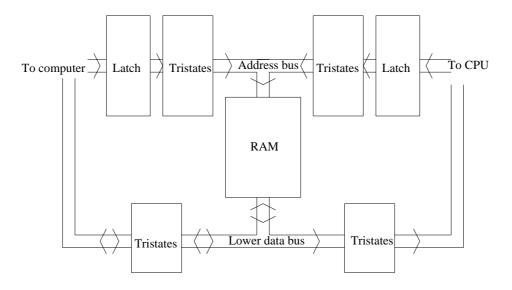

Some thought also needs to be put into how the system will connect to the computer. To ensure compatibility with as many models of computer as possible, it is best to use a standard interface. The two common interfaces are serial and parallel ports. In this case, the parallel port seems more useful, since its parallel outputs can drive directly the parallel data and address buses. The serial port would require an additional serial to parallel converter, which for an RS232 serial link is quite complex. This leaves the problem that the parallel port provides 5 digital inputs, 3 digital outputs, and 9 bidirectional digital lines, all of which can be independently controlled. This needs to be converted to 16 data lines, 13 address lines, the chip select pin and the write enable input. Since there are only 12 output lines on the port, it is not possible to write a full 16 bits at a time, so each chip has to be accessed individually. It would also be an advantage if the computer could read back the values it has written to the RAM, to check that they are correct. This means the tristates between the computer and the RAM's data bus need to be bidirectional. Since this section is acting as a ROM, it is better that the tristates between the RAM chip and the CPU data bus are unidirectional, so the processor is unable to corrupt the contents of the RAM chip. The address lines are only inputs to the RAM, so only need unidirectional tristates in either direction.

The limit of 12 outputs means that the address and data lines of each ROM chip cannot be controlled simultaneously, so multiplexing is required. It is therefore necessary to latch the address lines and then hold them steady while the data is read or written from the RAM. This is shown in the diagram below (only one RAM chip shown):

There are a large number of possible logic devices which could perform the functions in the above diagram. Two which appear suited to this situation are the 74LS245 'octal bus transceiver', which is basically two sets of eight tristates pointing in opposite directions, controlled by direction and enable pins, and the 74LS373 'octal transparent latch with 3-state outputs', which combines the latch and tristates on the address bus into a single chip. As the CPU side can drive all the address and data lines simultaneously, no latches are required. Therefore standard octal tristates can be used. The 74LS244 'octal buffer with 3-state outputs' performs this function and was to hand, so was used. This has two active low enable inputs, one for each of four tristates. All the tristates used here have Schmitt Trigger inputs, which improves their noise immunity.

These chips take up 8 of the 9 bidirectional parallel port pins. This leaves 4 possible outputs to select the relevant tristates and enable the RAM. One pin needs to be a direction, and so control the write enable lines and the bidirectional tristate direction input. The four tristate chips controlled by the computer each need to be accessed in turn. This requires further multiplexing. A counter could be used, but this would require a strict sequence of accessing to be followed. Two output lines can be converted to four by passing them through a one-of-four decoder to activate a device based on the binary code of the inputs. The 74LS139 does this, producing active low outputs. The latches have active high clock inputs and active low output enable inputs. In this application, the 74LS139 needs to be connected to their clock, so that to store data on them, it is written onto the parallel data lines, and the 139 activated to clock this onto the latches. The 74LS139 has an active low enable input, which takes all outputs high when it is deactivated. This switches off the computer side of the interface and allows the CPU to access the RAM. Another parallel port output is required to drive this, and to enable the latches' outputs to feed the address onto the ROM address bus. The remaining 1 output line can become a ROM select line, which is asserted when the computer wants to access the RAM chips, and enables everything associated with the computer interface.

Since the ROM select line coming out of the CPU's address decoding is active low, as is the output enable line on the RAM chip, the computer's ROM select should also be active low. If they were active high, the two select lines could be ORed together to produce a single OE input to the RAM. However, they are active low, so an AND is required:

OE = CS1 + CS2/OE = /(CS1+CS2) $/OE = /CS1 \bullet /CS2$

This leaves a problem. Only one RAM chip can be accessed at a time. For computer read cycles this does not matter, as half of the data bus outputs are ignored. However, for write operations, only half of the data is valid, as only one set of data bus tristates are enabled. With a common write line, one RAM chip will store invalid data. This could be got around simply by using another parallel port output line. However, all the possible outputs are in use.

When the computer is writing to the RAM, it enables one or other 74LS245, which feeds the data on the data bus into the relevant RAM chip. The 74LS245 is selected by an enable line from the 74LS139, which is controlled by two parallel port outputs. This can be used to route the write enable line to the RAM chip connected through to the data lines.

UWE = upper RAM chip write enable U245E = upper 74LS245 enable CWE = computer write enable output

UWE = U245E • CWE /UWE = /(U245E • CWE) /UWE = /U245E + /CWE

This is similar with the low RAM chip. /U245E is linked to the 245 in the active low form, so no inversion is required for it. The RAM chip needs an active low write strobe, which fits in with /UWE. This means the active high output from the computer has to be inverted to produce /CWE. It would be possible to adjust the programming software to pull CWE low to activate it, but due to the layout of the circuit on breadboard, it was more convenient to connect the RAM to the B side of the 74LS245s and the computer to the A side. Therefore to do a write the DIR pin, which is driven from the computer's write enable output, should be taken high to transmit data from A to B. This is the reverse of what the RAM requires, so an inverter will be required somewhere. This is an arbitrary decision, but it was decided to make CWE active low, as all the other signals in the system are also active low. Therefore /CWE needs to be inverted when connected to the direction input on the 74LS245s.

Combining all these elements produces the circuit below:

Copyright Theo Markettos 1997. This may be used for educational and non-profit making purposes only. The author may be reached at theomarkettos@letterbox.com

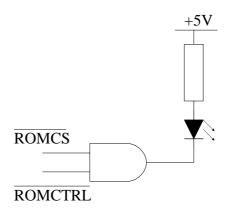

This section was tested by connecting it to a computer and then reading and writing data between the RAM and computer using the parallel port. The RAM did work, but this only tests the computer side of it. As a very basic test of the CPU side, the address lines were hardwired into a pattern, and /ROMCS asserted. A logic probe was then used to examine the output which would go onto the CPU data if it were connected. This showed it worked. However, I noticed that if both the computer was writing when the CPU was reading, the address lines of each would both drive the RAM data bus, so the contents of the RAM would become corrupted. The fault was indicated by ANDing /ROMCS and /ROMCTRL, which produces a low output if either is low:

CLASH = ROMCS + ROMCTRL /CLASH = /(ROMCS + ROMCTRL) /CLASH = /ROMCS • /ROMCTRL

The LED was connected between the AND gate output and +5V, so that it illuminates if a clash occurs:

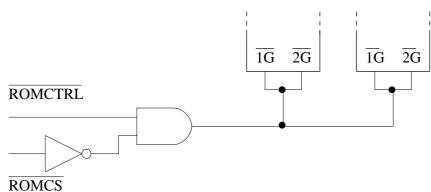

The memory corruption was prevented by using logic to disable the 74LS244s when the computer is accessing the RAM:

| /ROMCS | /ROMCTRL | 244 /ENABLE |

|--------|----------|-------------|

| 0      | 0        | 1           |

| 0      | 1        | 0           |

| 1      | 0        | 1           |

| 1      | 1        | 1           |

From this it can be seen the  $/244E = /ROMCTRL \bullet ROMCS$ . An AND gate was therefore used: Four 74LS244s

Copyright Theo Markettos 1997. This may be used for educational and non-profit making purposes only. The author may be reached at theomarkettos@letterbox.com

## **Initial testing**

Now that a fair proportion of the hardware was in place, basic testing could take place to see if there was anything seriously wrong.

The first test consisted of filling pages 0-3 (\$000 to \$3FF) with \$FFFFFFFF. These pages hold all the exception vectors, each of which points to a routine that the processor jumps to if it detects an error, which Motorola calls an exception. When reset, the processor reads the supervisor stack pointer from \$0 and the address of the code to call on reset from \$4. In this case both are \$FFFFFFFF, which are out of range addresses, so will trigger an address error, which involves it jumping to the address held at \$C. Since this also contains \$FFFFFFFF, an invalid address, the processor will go into 'double bus fault' mode, which means it will assert /Halt and then stop.

When the program was run by releasing the reset button, the Reset LED was off, Halt was on, and the function code LEDs showed 110, which fits in with the above process. This provides one piece of evidence that the system is working.

The next test involved setting all the exception vectors to \$00000400, a valid address in ROM. \$0, the supervisor stack pointer, was set to \$42000, an address in the middle of RAM. This now allows the processor to run code from \$400 when it is reset. The instruction STOP was loaded at \$400. When run, this program turned off both the Reset and Halt LEDs, and set the function code LEDs to 101. These can be interpreted as shown in Appendix A figure 3-3. A 101 state shows that the processor is not fetching instructions, so is stopped.

A slightly longer program was assembled and loaded at \$400:

| 00000400 |      | 1 |      | ORG \$400  |

|----------|------|---|------|------------|

| 00000400 | 4E71 | 2 | loop | NOP        |

| 00000402 | 60FC | 3 |      | BRA.S loop |

| 00000404 |      | 4 |      |            |

This is an endless loop that does nothing. When run, Reset and Halt were off, and the function code LEDs showed 111. This relates to a CPU space cycle, which should happen very rarely. When examined with an oscilloscope, it was found that both FC0 and FC1 were rapidly changing state, which would show up as a dim LED. This seems to suggest that the program is alternating between supervisor data and program accesses.

All the tests so far would not show if any errors were occurring, since, if an error occurred, the processor would examine the relevant exception vector and jump straight back to the start of the code at \$400. To see if any errors were occurring, the address exception vector was set to \$FFFFFFF. The other vectors were then overwritten one by one with \$FFFFFFFF, and the program tested after each one. The idea behind this is that if an error occurs, the program will examine the relevant exception vector, find it to contain an invalid address, and so cause an Address Error. Since the Address Error vector also contains an invalid address, the processor stops with a double bus fault as before. By overwriting the exception vectors one by one, it is possible to work out which exception vector, if any, is being triggered.

When this was done, it was found that the processor was calling the Illegal Instruction vector. By modifying the program at \$400, it was possible to determine that the processor objected to bit 14 being set in \$60FC, the BRA.S loop instruction. This suggests a problem with the high data bus. The data bus from the ROM 74LS244s to the processor was examined, and it was found that bit 14 was connected to bit 10 by mistake, so the processor was reading the instruction as \$00FC, which is an illegal instruction.

Having rectified this fault, another simple program was tried. This now goes into user mode by clearing status register bit 13, and then goes into an endless loop. If it works without any exception vectors being called, the supervisor LED, which is connected to FC2, should stay extinguished.

| 00000400 |           | 1 |      | ORG \$400    |

|----------|-----------|---|------|--------------|

| 00000400 | 46FC 0000 | 2 |      | MOVE.W #0,SR |

| 00000404 | 4E71      | 3 | loop | NOP          |

| 00000406 | 60FC      | 4 |      | BRA.S loop   |

This did happen, proving the system was working.

## **Digital inputs and outputs**

Having now got the main microprocessor system working, its inputs and outputs can now be considered. The simplest of these are the digital output (connected to a bank of LEDs) and the digital input (connect to a bank of DIP switches).

#### **Digital output**

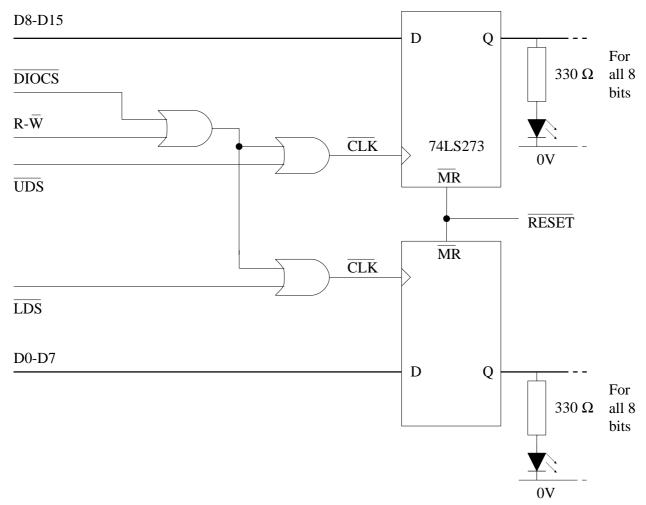

This output is to drive a bank of LEDs as a general purpose output port. Since the 68000's data bus is 16 bits wide, it is useful to have a 16 bit wide display, so that any number which can be represented on the data bus can be shown on the display. As the 68000 uses /LDS and /UDS to signify which data lines are valid, the display can also be treated as two independent 8 bit displays.

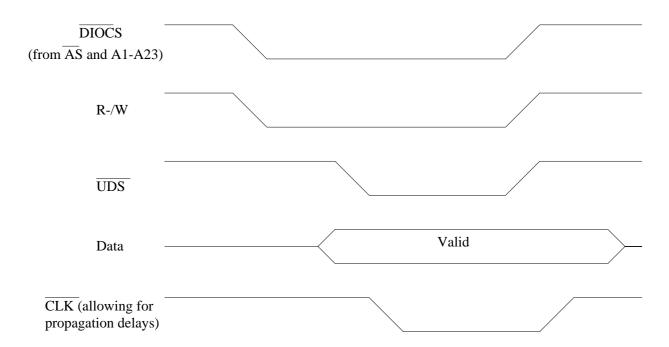

To do this requires a latch, which will hold the data steady when it is not being written to. The address decoding circuitry needs to be arranged to clock this latch when the output port is being written to, which will transfer the data value from the data bus onto the outputs. For each half to be accessible individually, each eight bits needs a separate clock signal. Since there are no 16-bit latch chips available, two 8-bit latches will have to be used instead. The device must have an asynchronous reset, so that it will come into a known state when the system is powered up, otherwise it could inadvertently switch on devices connected to the outputs such as heaters or alarm systems.

There is only one widely available device that fits this specification, the 74LS273. This is a D-register, not a latch, which means that it is edge, not level, triggered. In this situation this is an advantage, because when the latch is first triggered the valid data may not have reached it, due to propagation delays through other components. A D-register can be triggered on the edge when the chip enable signal is negated, which allows ample time for the data to be valid. According to the 68000 User's Manual, there is 40ns between /UDS and /LDS being negated and the data becoming invalid. The 'FAST and LS TTL data book' says that 74LS273 needs the data to be stable for 5ns after it has been clocked, so this will work.

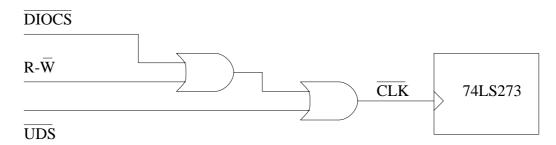

Taking the high data bus D-register (bits D8-D15), the register needs to be clocked when UDS is high, DIOCS is high and R-/W is low:

CLK = UDS • DIOCS • /R-W /CLK = /(UDS • DIOCS • /R-W) /CLK = /UDS + /DIOCS + R-/W

/UDS, /DIOCS, and R-/W are the signals actually available from the CPU and address decoding. In the above equation, CLK will go low only if all three conditions are satisfied. As soon as one is released, CLK will go high. This is shown by the following timing diagram:

The register is rising edge triggered, so triggers on the rising edge of /CLK. Thus the register will be clocked with valid data.

The Boolean expression describes the following logic system:

2-input OR gates have to be used because these are the only type available in the 74 series or its variants. For the low data bus the system would be the same, except using /LDS instead of /UDS. Since the top OR gate is common to both, its output can be shared between each system.

The final circuit constructed was as below:

This was tested with the following program which performs a binary count on the LEDs:

| 00000400 |      |          | 1  |        | ORG \$40 | 00            |   |                       |

|----------|------|----------|----|--------|----------|---------------|---|-----------------------|

| 00000400 | 46FC | 0000     | 2  |        | MOVE.W   | #0,SR         | * | Go into user mode     |

| 00000404 |      |          | 3  | main   |          |               |   |                       |

| 00000404 | 7000 |          | 4  |        | MOVEQ    | #0,D0         | * | Clear DO              |

| 00000406 |      |          | 5  | main_  | loop     |               |   |                       |

| 00000406 | 5240 |          | 6  |        | ADDQ.W   | #1,D0         | * | Increment D0          |

| 00000408 | 33C0 | 00080600 | 7  |        | MOVE.W   | D0,\$80600    | * | Output D0 to all LEDs |

| 0000040E | 223C | 0000FFFF | 8  |        | MOVE.L   | #\$FFFF,D1    | * | Amount of time to     |

|          |      |          |    |        |          |               |   | waste                 |

| 00000414 |      |          | 9  | delay_ | _loop    |               |   |                       |

| 00000414 | 51C9 | FFFE     | 10 |        | DBF      | D1,delay_loop | 0 | * Decrement D0, waste |

|          |      |          |    |        |          |               |   | time if not zero      |

| 00000418 |      |          | 11 |        |          |               |   |                       |

| 00000418 | 60EC |          | 12 |        | BRA.S    | main_loop     | * | loop round            |

|          |      |          |    |        |          |               |   |                       |

This shows that the LEDs were working by displaying a binary count on them. From the order they were being illuminated, it could be seen that some of the data connections were wrong. After examination, it was found that lines D0-D4 were twisted so that LED 0 was connected to D4, LED 1 to D3 and so on. Once this was fixed, the LEDs displayed a proper count. By changing the pin of the 74LS161 that the master clock was connected to, it was possible to see the effect of different clock speeds. All from 8 to 1 MHz worked, although 1 and 2 MHz may not be very reliable, or work on all 68000 chips.

Copyright Theo Markettos 1997. This may be used for educational and non-profit making purposes only. The author may be reached at theomarkettos@letterbox.com

#### **Digital input**

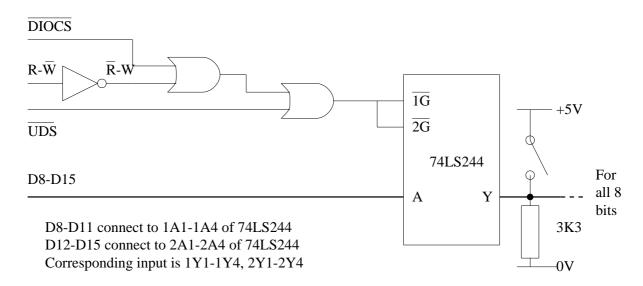

Now that there is an output to display it on, the digital inputs can be considered. It was decided to have an 8-bit input port which would initially be connected to a bank of DIP switches, but could be connected to other devices if necessary. The bank of DIP switches are handy for giving the system basic configuration information, such as initial serial data rate or which mode to start up in.

The input hardware is basically the same as for the outputs except operating in the opposite direction. Since the signals will be present from the input sources whether the CPU is reading them or not, latching is not necessary. What is required is a tristate to buffer the inputs and connect them through to the data bus when the CPU is reading them. For this any 8 bit tristate will do, so the 74LS244 was chosen as before.

As only 8 bits are required, it seems neater to have them mapped to address \$80600 rather than \$80601. Since the 68000 stores the high byte of a two byte word at the lower address, \$80600 refers to data lines D8 to D15 during a read. Therefore the tristates have to be connected to D8-D15, and are activated when /UDS is asserted. The 74LS244 enables are active low, so the LED chip enable hardware can be used here, with an inverted R-/W, so it is activated on a read not a write:

/R-W is a common signal, so, since the fanout of the inverter used (a 74LS04) is very large, it can drive any other device that needs it.

This was tested by reading the inputs and outputting them on the LEDs:

| 00000400 |                    | 1 | ORG \$40 | 0          |                         |

|----------|--------------------|---|----------|------------|-------------------------|

| 00000400 | 46FC 0000          | 2 | MOVE.W   | #0,SR      | * Go into user mode     |

| 00000404 |                    | 3 | main     |            |                         |

| 00000404 | 33FC 0000 00080600 | 4 | MOVE.W   | #0,\$80600 | * Blank LEDs            |

| 0000040C |                    | 5 | loop     |            |                         |

| 0000040C | 1039 00080600      | б | MOVE.B   | \$80600,D0 |                         |

| 00000412 | 13C0 00080600      | 7 | MOVE.B   | D0,\$80600 | * Copy DIP switch value |

|          |                    |   |          |            | to LEDs                 |

| 00000418 | 60F2               | 8 | BRA.S    | loop       |                         |

Copyright Theo Markettos 1997. This may be used for educational and non-profit making purposes only. The author may be reached at theomarkettos@letterbox.com

## **Exception vector code**

Now the LEDs are working, the handling of exceptions can be improved. Currently, they just cause the program to restart if an exception occurs, which is not ideal. It is better to have some display that an exception occurs. This could be achieved by displaying the vector number, plus a recognisable flashing sequence of some kind to indicate that an exception occurred.

The main problem with this is how to load the vector number into a register. When an exception occurs, the CPU loads the address stored at the exception vector, and jumps to it. When it has done the jump, there is no record of which exception occurred. If all the exception vectors pointed to the same address, it would not be possible to work out what type of exception was detected.

Therefore, each exception vector must point to a separate routine to load the number into a register. The neatest solution would be to have a long series of ADD instructions, so that the relevant number were executed, adding the exception vector number onto a data register. The problem is that there is no way of setting the register to zero in the first place.

The simplest way, therefore, is for each exception vector to point to a separate routine that loads a register with the number of the exception, and then jumps to a main routine. This is what was done:

Address:

| 8<br>C<br>10                                         | DC.L<br>DC.L<br>DC.L                                                     | \$108<br>\$10C<br>\$110                                            | <ul><li>* exception vector table</li><li>* - all point to routine to set</li><li>* D0 to vector number</li></ul>               |

|------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 7C                                                   | DC.L                                                                     | \$17C                                                              |                                                                                                                                |

| 108<br>10A<br>10C<br>10E<br>110<br>112<br>17C<br>17E | MOVEQ<br>BRA.S<br>MOVEQ<br>BRA.S<br>MOVEQ<br>BRA.S<br><br>MOVEQ<br>BRA.S | <pre>exception #\$C,D0 exception #\$10,D0 exception #\$7C,D0</pre> | * code to set D0 to exception<br>* vector number as pointed to above                                                           |

| exception<br>180<br>186                              | MOVE.B                                                                   | D0,\$80600<br>#-1,D0                                               | <ul> <li>* write exception code on high LEDs</li> <li>* initial value to store on low LEDs</li> <li>* (turn all on)</li> </ul> |

| excep_loo<br>18A<br>190<br>192                       | MOVE.B<br>NOT                                                            | D0,\$80601<br>D0<br>#\$FFFF,D1                                     | * store on low LEDs<br>* invert D0<br>* loop variable                                                                          |

| excep_tim<br>196<br>19A                              | e_loop<br>DBF<br>BRA.S                                                   | D1,excep_time_loop<br>excep_loop                                   | * decrement and loop (waste time)                                                                                              |

This stores the exception code on the high LEDs and flashes all the low LEDs in unison. The only way out of this is to reset the processor. This did work, and running a program when this was in place showed that no exceptions were occurring. An exception was caused by taking one of the IPL lines low, causing an interrupt. This showed as an address error, as there was no interrupt hardware present, but showed the exception code was working.

## 6800 series bus cycles

Apart from the digital I/O, all the other inputs and outputs are serviced by 6800 series peripheral ICs. These predate the 68000. and require the 68000 to modify its bus cycle to access them. The basic access cycle is detailed below:

- 1 Processor starts a normal read or write cycle

- 2 External hardware asserts Valid Peripheral Address (/VPA)

- 3 Processor wait until clocks are synchronised and then asserts Valid Memory Address (/VMA)

- 4 The peripheral waits until E is active and then transfers the data

- 5 The processor negates /AS, /UDS, /LDS and drives the E clock low

- 6 The processor negates /VMA

In essence, /VPA is provided by the address decoding to tell the 68000 that it is accessing a 6800 series device, and then /VMA from the processor behaves as one chip enable signal, and E supplies a clock to the device, at 1/10 of the processor clock frequency.

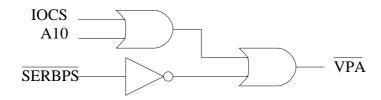

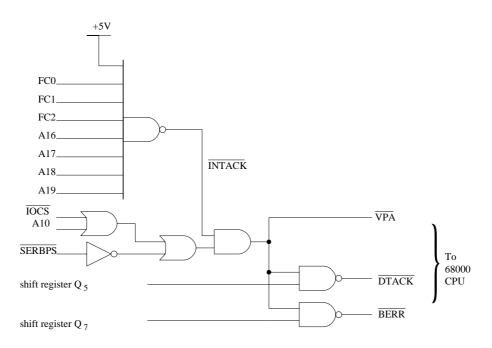

Therefore the only signal that needs to be worried about is /VPA. The address decoding was organised so that I/O devices from \$80000 to \$803FF need to have /VPA asserted. Therefore /VPA can be represented as follows:

$VPA = IOCS \cdot /A10$

A10 is low when an address in the range \$000 to \$3FF is being accessed. This expression can be converted to the logic signals required by the system by inverting it:

| /VPA = /IOCS + A10 A10 | $/VPA = /(IOCS \cdot /A10)$<br>/VPA = /IOCS + A10 | IOCS     A10 | VPA |

|------------------------|---------------------------------------------------|--------------|-----|

|------------------------|---------------------------------------------------|--------------|-----|

This will give a working /VPA signal, but it could be improved. In the 6850 serial chip's address space, there is provision for a baud rate selector at \$80004. This would not be a 6800 series IC, so does not need a special access cycle. It is likely that it would work with a 6800 cycle, but this would slow access down for no purpose.

The baud rate selector is active when /SERBPS is asserted, so this can be combined into the above logic system.

| old /VPA | /SERBPS | new /VPA |

|----------|---------|----------|

| 0        | 0       | 1        |

| 0        | 1       | 0        |

| 1        | 0       | 1        |

| 1        | 1       | 1        |

Therefore:

/newVPA = SERBPS + /oldVPA

This gives the following circuit diagram:

When this was constructed, it was tested by writing a short program to access a 6800 series device address. This apparently worked when accessing \$80004, but crashed with a Bus Error when accessing any other address from \$80000 to \$803FF. There is no way of testing the system completely at the moment, as there are no 6800 devices in the system at the moment, but it should just return a value representing whatever noise happened to be on the data bus at the time.

Careful study of the 6800 chapter in the 68000 User's Manual brought the following paragraph to my attention:

'Data transfer acknowledge (/DTACK) must not be asserted while /VPA is asserted. The state machine in the processor looks for /DTACK to identify an asynchronous bus cycle and for /VPA to identify a synchronous peripheral bus cycle. If both signals are asserted, the operation of the state machine is unpredictable.'

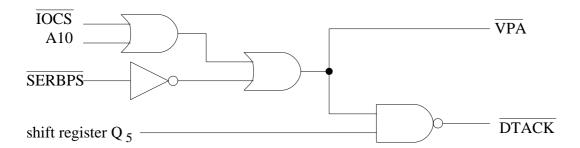

/DTACK is being generated automatically from the shift register. Therefore /VPA will be asserted first, as it is determined by the reasonably fast address decoding system, and then part way through the 6800 access cycle, the shift register asserts /DTACK, which confuses the processor. External logic is required to disable /DTACK when /VPA is asserted. It would be dangerous to use /VPA to reset the shift register, because when it comes out of reset, the shift register will start shifting ones through itself at the end of a bus cycle, which might spuriously trigger /DTACK or /BERR. The signal /DTACK will therefore have to be gated after it comes out of the shift register:

| old /DTACK | /VPA | new /DTACK |

|------------|------|------------|

| 0          | 0    | 1          |

| 0          | 1    | 0          |

| 1          | 0    | 1          |

| 1          | 1    | 1          |

Thus: /newDTACK = /oldDTACK + VPA

Since /oldDTACK is an inverted form of  $Q_5$  from the shift register, the inverter can be cancelled out:

newDTACK = /(/oldDTACK + VPA) newDTACK = oldDTACK • /VPA /newDTACK = /(oldDTACK • /VPA)

This reduces two inverters to one, and if a NAND gate chip is used, means only one gate is required:

When this was constructed, it was found that the bus error was still being caused. After thinking about the problem, I realised that /BERR was being triggered in the middle of the /VPA bus cycle. /BERR is triggered 8 clock cycles after the start of the bus cycle, while the /VPA bus cycle takes 10 clock cycles. This means that any VPA cycle will cause a bus error, as /BERR is triggered before the cycle has finished.

This could be prevented by extending the shift register, so /BERR is asserted after a VPA cycle should have finished. This, however, prevents /BERR from working with normal /DTACK based bus cycles. The alternative is to simply disable /BERR when a VPA cycle is in progress, as shown above with /DTACK. This is much simpler, and requires a great deal less logic.

The logic is precisely the same as with /DTACK, as they both come from the same source:

When tested, this did not give any bus errors, although it is difficult to test it without any 6800 devices present.

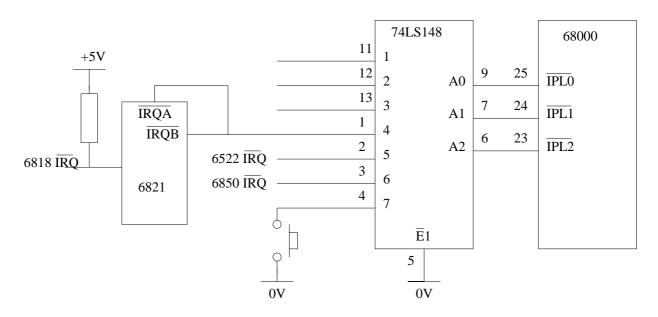

## 6800 series peripherals

Now the bus support is in place, it is a relatively simple matter to connect the 6800 series peripherals into the system.

### 6821 Peripheral Interface Adapter

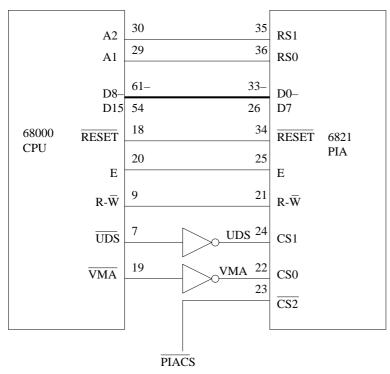

The bus interface of the 6821 consists of an 8 bit data bus, two register select lines, a /RESET line, three chip enable pins, an E clock and a R-/W input.

The /RESET, E and R-/W are the same signals that are output from the processor, so can be connected directly. Due to the 68000's policy of accessing low addresses on the high data bus, the 6821's D0-D7 need to be connected to the 68000's D8-D15, so that the 6821 can be accessed at even addresses \$80200, \$80202 and so on, instead of \$80201, \$80202, etc. This is a cosmetic feature, but it makes programs look neater if they are accessing \$80200 instead of \$80201.

The register select inputs (RS0 and RS1) can be connected to low order address lines, so the registers can be accessed at consecutive addresses. As A0 is not available due to the 16 bit bus, RS0 can go to A1 and RS1 to A2, so the 6821 appears at addresses \$80200, \$80202, \$80204 and \$80206.

This leaves the three chip select inputs, CS0, CS1 and /CS2. This is convenient because there are three signals which all need to be asserted for the chip to be activated, /VMA, /UDS and /PIACS. As there is only one active low input, two will have to be inverted. Since /PIACS will not be used anywhere else in the system, whereas /VMA and /UDS are, it seems more useful to invert /VMA and /UDS, since VMA and UDS could be used elsewhere, and this would save on logic.

The connections of the 6821 are summarised below:

Copyright Theo Markettos 1997. This may be used for educational and non-profit making purposes only. The author may be reached at theomarkettos@letterbox.com

The PIA was tested by configuring Ports A and B as inputs, and then reading them and displaying the value on the LEDs:

| 000000000000000000000000000000000000000 |       |          | 1<br>2 | * 6821 Pe | eripheral I  | inte | erface Adapter test          |

|-----------------------------------------|-------|----------|--------|-----------|--------------|------|------------------------------|

| 00000000                                |       |          | 2<br>3 |           | a ugar mada  | 、 .  | initialise PIA as inputs.    |

| 00000000                                |       |          | 3<br>4 |           |              |      | write to LEDs.               |

| 00000000                                |       |          | 5      | Reau P.   | IA POILS all | ia v | WIICE CO LEDS.               |